For navigation instructions please click here

Search Issue

Next Page

Innovative Technology for Computer Professionals

# NOVEMBER 2011 .--

http://www.computer.org

# CODESIGN FOR SYSTEMS AND APPLICATIONS

HUMAN EAR RECOGNITION, P. 79 CROWDSOURCING MAPS, P. 90 AUTOMATED PERSONAL ASSISTANTS, P. 112

Contents

Zoom in | Zoom out

II

Search Issue

Next Page

Previous Page | Contents | Zoom in | Zoom out | Front Cover | Search Issue | Next Page

# **Announcement of the 2nd International Call for Research Projects** within the ERA-Net CHIST-ERA

Deadline for proposal Submission: 17th of January 2012 (17:00 GMT)

CHIST-ERA Stands for European Coordinated Research on Long-term Challenges in Information and Communication Sciences and Technologies ERA-Net

chist-era call 2011

The CHIST-ERA initiative is looking for highly innovative and multidisciplinary collaborative projects in ICST. Especially CHIST-ERA is open to new ideas and original solutions, involving interdisciplinary skills. In addition, the transformative research done in CHIST-ERA shall explore new topics with potential for significant scientific and technical impacts. The projects must involve at least three partners from three different and participating countries. In the Call 2011, two new and hot topics are addressed:

# From Data to New Knowledge

The challenge is to produce new computational concepts, models, tools and methodologies to automatically and reliably extract new knowledge from large amounts of heterogeneous, unstructured data. Typical data include multilingual and multimedia data such as found on the web (text, speech, image, video, ...) and data generated by human organisations in the course of scientific, industrial or service activities (medical data, 3D object representations, advanced manufacturing data, ...). Though much activities are already going on in the field, existing systems are far from offering a highly reliable extraction of knowledge from any type of data, and basic research is still needed to explore new concepts and models for challenging tasks such as machine reading, processing of noisy data, multiscale model handling...

The decrease of energy consumption for computation or communication is an important challenge for future. In addition this renders possible the design of autonomous systems scavenging their own energy from their environment. A broad range of solutions are currently envisaged from component to system of systems levels, where research is needed in various areas. Project proposals should address the issue of energy consumption in computation, information, sensing or communication systems from a global system perspective. Highly innovative approaches are expected at any of the system layers, from the nano-scale level to the architectural, software or protocol layers...

### Call Information: www.chistera.eu

Disclaimer:

retugmeD

the information in this announcement is provided as is and no guarantee or warranty is given that the information is fit for any particular purpose. The user therefore uses the information at its sole risk and liability.

Previous Page | Contents | Zoom in | Zoom out | Front Cover | Search Issue | Next Page

# nnovative Technology for Computer Professionals nputer

### **Editor in Chief**

**Ron Vetter** University of North Carolina Wilmington vetterr@uncw.edu

### **Associate Editor** in Chief Sumi Helal University of Florida helal@cise.ufl.edu

**Area Editors Computer Architectures** Tom Conte Georgia Tech Steven K. Reinhardt AMD **Distributed Systems** Jean Bacon University of Cambridge **Graphics and Multimedia Oliver Bimber** Johannes Kepler University Linz **High-Performance Computing Vladimir Getov** University of Westminster Information and **Data Management** Naren Ramakrishnan Virginia Tech Multimedia Savitha Srinivasan IBM Almaden Research Center Networking Ahmed Helmv University of Florida **Security and Privacy Rolf Oppliger** eSECURITY Technologies Software **Robert B. France** Colorado State University David M. Weiss Iowa State University **Web Engineering** Simon Shim

San Jose State University

### **Editorial Staff Judith Prow** Managing Editor jprow@computer.org Chris Nelson Senior Editor

Associate Editor in Chief, **Research Features** Kathleen Swigger University of North Texas kathy@cs.unt.edu

### Associate Editor in Chief, Special Issues

**Bill N. Schilit** Google schilit@computer.org

### **Column Editors**

**Discovery Analytics** Naren Ramakrishnan Virginia Tech Education Ann E.K. Sobel Miami University **Entertainment Computing Kelvin Sung** University of Washington, Bothell Green IT Kirk W. Cameron Virginia Tech **Identity Sciences** Karl Ricanek University of North Carolina, Wilmington **In Development Chris Huntley** Fairfield University **Industry Perspective** Sumi Helal University of Florida **Invisible Computing** Albrecht Schmidt University of Stuttgart The Known World David A. Grier George Washington University **The Profession** Neville Holmes University of Tasmania Security Jeffrey M. Voas NIST

### **Computing Practices Rohit Kapur** Synopsys

rohit.kapur@synopsys.com

Perspectives Bob Colwell bob.colwell@comcast.net

**Social Computing** John Riedl University of Minnesota **Software Technologies Mike Hinchey** Lero—the Irish Software **Engineering Research Centre**

### **Advisory Panel**

Carl K. Chang Editor in Chief Emeritus Iowa State University Hal Berghel University of Nevada, Las Vegas **Doris L. Carver** Louisiana State University **Ralph Cavin** Semiconductor Research Corp. **Rick Mathieu** James Madison University Naren Ramakrishnan Virginia Tech **Theresa-Marie Rhyne** Consultant Alf Weaver University of Virginia

Web/Multimedia Editor Charles R. Severance csev@umich.edu

2011 IEEE Computer Society President Sorel Reisman s.reisman@computer.org

### **Publications Board**

David A. Grier (chair), Alain April, David Bader, Angela R. Burgess, Jim Cortada, Hakan Erdogmus, Frank E. Ferrante, Jean-Luc Gaudiot, Paolo Montuschi, Dorée Duncan Seligmann, Linda I. Shafer, Steve Tanimoto, George Thiruvathukal

### **Magazine Operations** Committee

Dorée Duncan Seligmann (chair), Erik R. Altman, Isabel Beichl, Krishnendu Chakrabarty, Nigel Davies, Simon Liu, Dejan Milojičić, **Michael Rabinovich, Forrest** Shull, John R. Smith, Gabriel Taubin, Ron Vetter, John Viega, Fei-Yue Wang, Jeffrey R. Yost

### **Contributing Editors Camber Agrelius** Lee Garber **Bob Ward**

### Larry Bauer Design Olga D'Astoli Cover Design Kate Wojogbe Jennie Zhu

**Design and Production**

**Administrative**

Staff **Products and Services Director** Evan Butterfield Senior Manager. **Editorial Services** Lars Jentsch

Manager, **Editorial Services** Jennifer Stout **Senior Business Development Manager** Sandy Brown Senior Advertising Coordinator Marian Anderson

Circulation: Computer (ISSN 0018-9162) is published monthly by the IEEE Computer Society. IEEE Headquarters, Three Park Avenue, 17th Floor, New York, NY 10016-5997; IEEE Computer Society Publications Office, 10662 Los Vaqueros Circle, Los Alamitos, CA 90720-1314; voice +1 714 821 8380; fax +1 714 821 4010; IEEE Computer Society Headquarters, 2001 L Street NW, Suite 700, Washington, DC 20036. IEEE Computer Society membership includes \$19 for a subscription to Computer magazine. Nonmember subscription rate available upon request. Single-copy prices: members \$20; nonmembers \$99.

Postmaster: Send undelivered copies and address changes to Computer, IEEE Membership Processing Dept., 445 Hoes Lane, Piscataway, NJ 08855. Periodicals Postage Paid at New York, New York, and at additional mailing offices. Canadian GST #125634188. Canada Post Corporation (Canadian distribution) publications mail agreement number 40013885. Return undeliverable Canadian addresses to PO Box 122, Niagara Falls, ON L2E 6S8 Canada. Printed in USA

Editorial: Unless otherwise stated, bylined articles, as well as product and service descriptions, reflect the author's or firm's opinion. Inclusion in Computer does not necessarily constitute endorsement by the IEEE or the Computer Society. All submissions are subject to editing for style, clarity, and space.

### **NOVEMBER 2011**

retugmed

Qmags

1

**Innovative Technology for Computer Professionals** www.computer.org/computer

# ABOUT THIS ISSUE

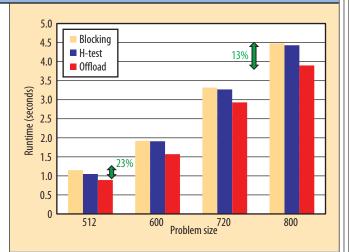

he essence of the codesign challenge for exascale systems is to use the key design criteria of embedded systems—cost and power consumption—while creating systems that are useful and effective over the broad range of applications needed to advance science. The cover features in this special issue have been selected to cover a cross-section of the codesign space and the relevant concerns and challenges.

### **COVER FEATURES**

**GUEST EDITORS' INTRODUCTION 19** Codesign for Systems and **Applications:** Charting the Path to Exascale Computing Vladimir Getov, Adolfy Hoisie,

### and Harvey J. Wasserman

The clock speed benefits of Moore's law have ended, and researchers must codesign future exascale HPC systems and applications concurrently in an integrated manner to achieve higher performance under stringent power and reliability constraints.

### 22 Rethinking Hardware-Software **Codesign for Exascale Systems**

### John Shalf, Dan Quinlan,

and Curtis Janssen

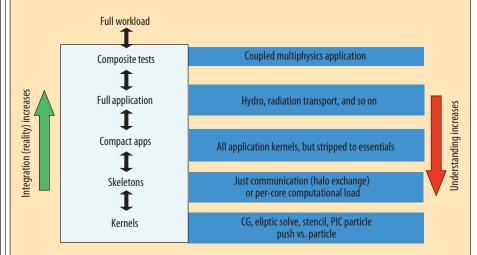

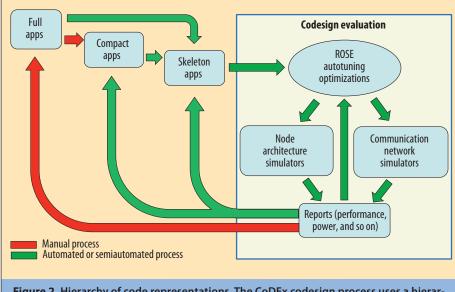

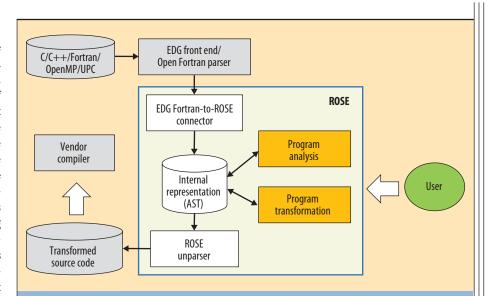

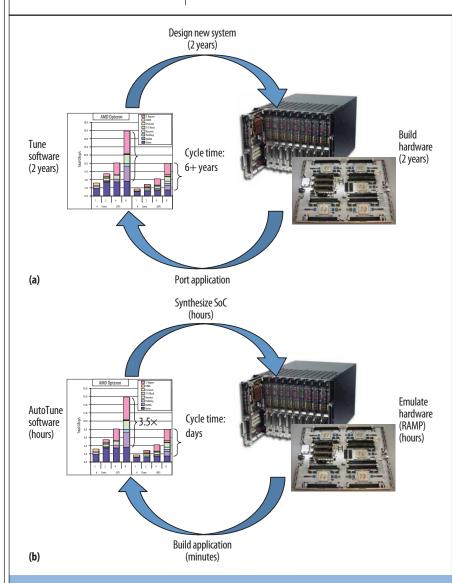

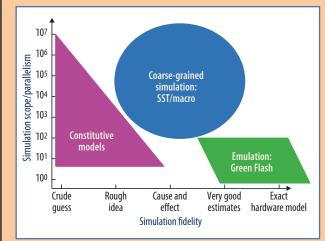

The US Department of Energy's exascale computing initiative has identified hardwaresoftware codesign as a central strategy in achieving more agile hardware development. Hardware simulation and code analysis tools that facilitate deeper collaboration between hardware architects and application teams will be an essential component of the codesign process.

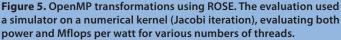

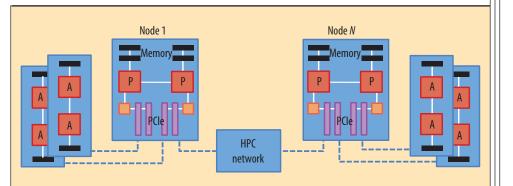

# **31** Codesign for InfiniBand

### Clusters Sayantan Sur, Sreeram Potluri, Krishna Kandalla, Hari Subramoni,

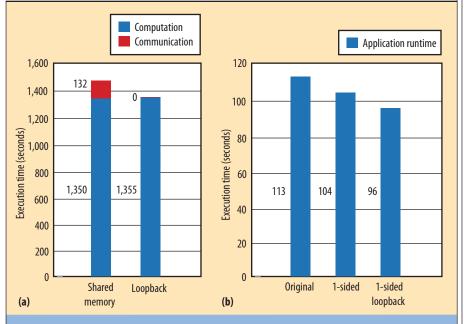

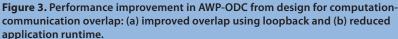

Dhabaleswar K. Panda, and Karen Tomko Codesigning applications and communication libraries to leverage underlying network features is imperative for achieving optimal performance on modern computing clusters.

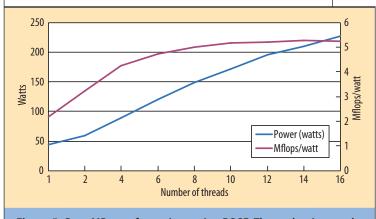

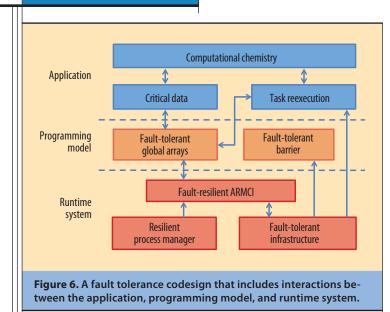

### **37** Codesign Challenges for **Exascale Systems: Performance, Power, and Reliability**

### Darren J. Kerbyson, Abhinav Vishnu, Kevin J. Barker, and Adolfy Hoisie

The complexity of large-scale parallel systems necessitates the simultaneous optimization of multiple hardware and software components to meet performance, efficiency, and fault-tolerance goals. A codesign methodology using modeling can benefit systems on the path to exascale computing.

### **COMPUTING PRACTICES**

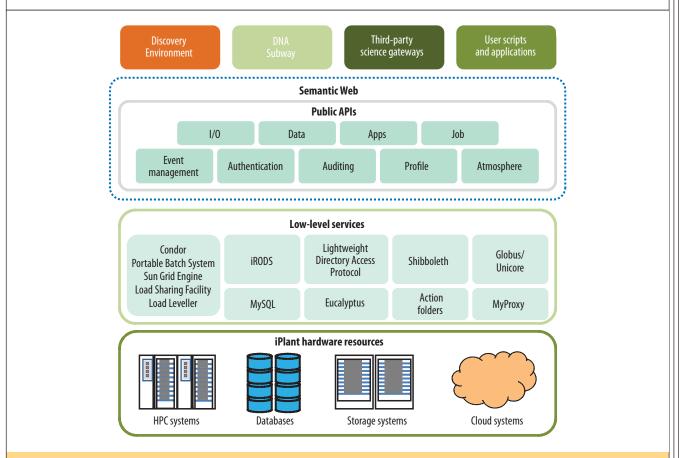

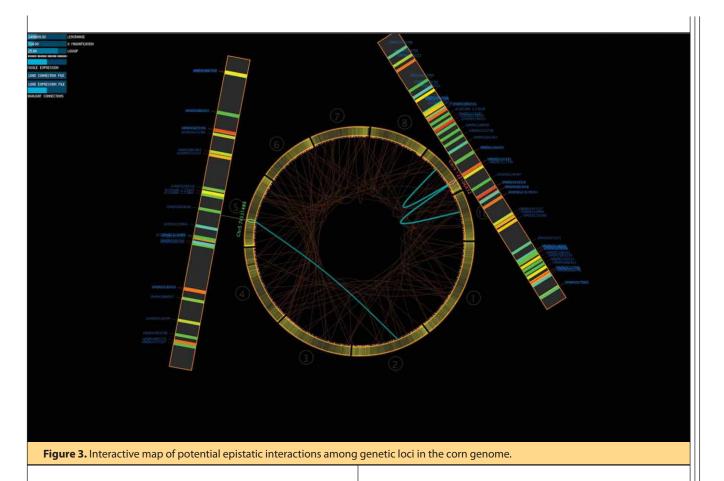

### **44** The iPlant Collaborative: **Cvberinfrastructure to Feed** the World

### **Dan Stanzione**

As plant biology becomes a data-driven science, new computing technologies are needed to address many formidable challenges. The iPlant Collaborative provides cyberinfrastructure for researchers and developers to collaborate in creating better tools, workflows, algorithms, and ontologies.

### PERSPECTIVES

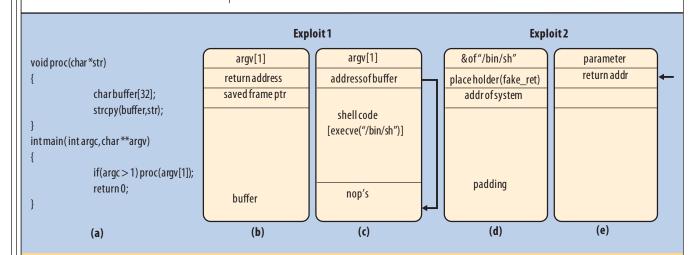

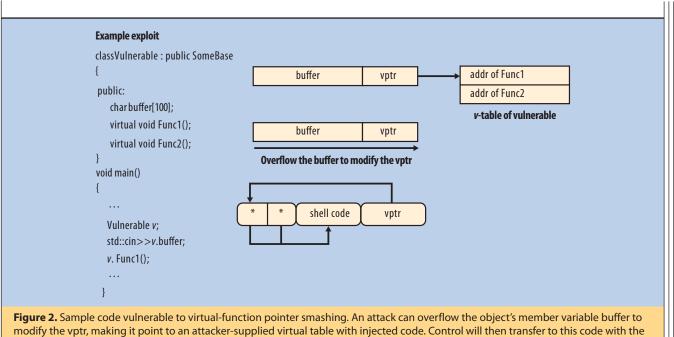

### **53** Defending against Buffer-**Overflow Vulnerabilities**

# Bindu Madhavi Padmanabhuni

and Hee Beng Kuan Tan

A survey of techniques ranging from static analysis to hardware modification describes how various defensive approaches protect against buffer overflow, a vulnerability that represents a severe security threat.

### **RESEARCH FEATURE**

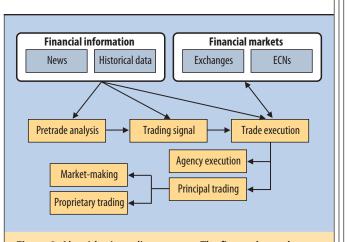

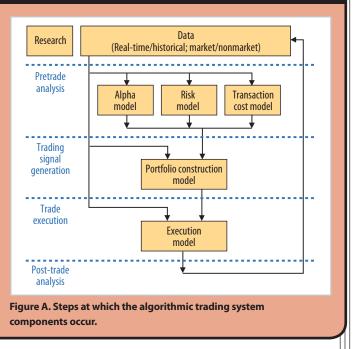

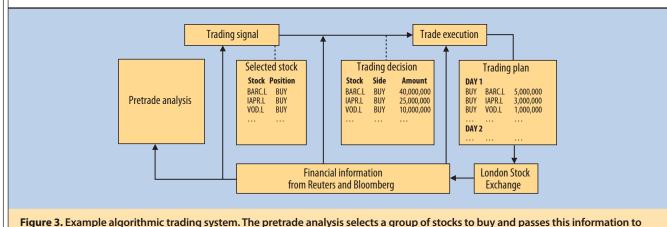

### **61** Algorithmic Trading Giuseppe Nuti, Mahnoosh Mirghaemi, Philip

# Treleaven, and Chaiyakorn Yingsaeree

Traders increasingly use automated systems for one or more stages of the trading process, yet the secrecy and complexity of the algorithms prompt providing an overview of how these systems work.

For more information on computing topics, visit the Computer Society Digital Library at www.computer.org/csdl.

ഗ

Qmags

IEEE Computer Society: http://computer.org Computer: http://computer.org/computer computer@computer.org IEEE Computer Society Publications Office: +1 714 821 8380

# **The Known World**

The Honest Give-and-Take **David Alan Grier**

### 32 & 16 Years Ago

Computer, November 1979 and 1995 **Neville Holmes**

### **NEWS**

### **11** Technology News

Turning on the Lights for Wireless Communications Lee Garber

**15** News Briefs Lee Garber

### MEMBERSHIP NEWS

**70** IEEE Computer Society **Connection**

### 73 Call and Calendar

### COLUMNS

### 75 Green IT

End-to-End Energy Management Yung-Hsiang Lu, Qinru Qiu, Ali R. Butt, and Kirk W. Cameron

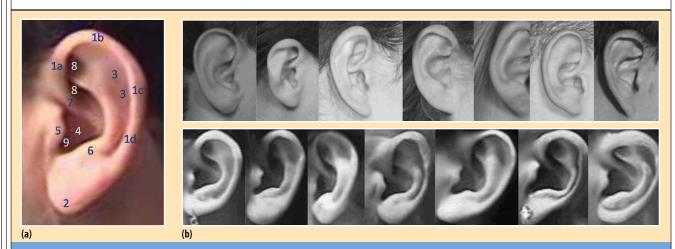

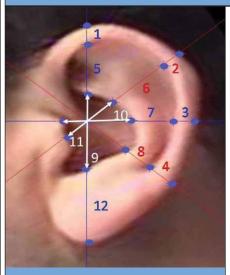

### 79 Identity Sciences

Human Ear Recognition **Arun Ross and Ayman Abaza**

See www.computer.org/computermultimedia for multimedia content related to the features in this issue.

Printed with inks containing

soy and/or vegetable oils

SUSTAINABLE FORESTRY INITIATIVE

### Flagship Publication of the IEEE **Computer Society**

November 2011, Volume 44, Number 11

### 83 **Industry Perspective**

**Opportunities in the Mobile Search Market** José Luis Gómez-Barroso, Claudio Feijóo, and Ramón Compañó

### 87 Hard Issues

If Anything in This Life Is Certain, It's That You Can Kill Any ISA Shubu Mukherjee

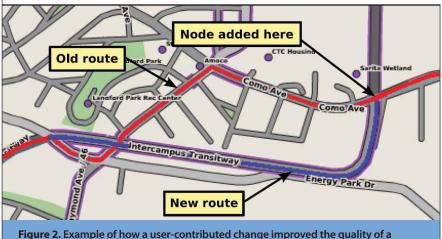

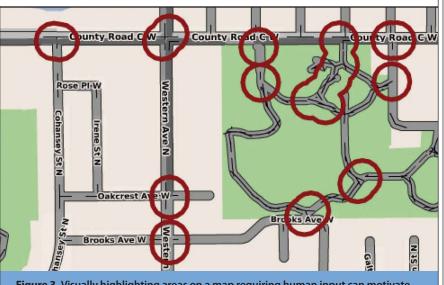

90 **Social Computing Crowdsourcing Maps Mikhil Masli**

### **112** The Profession

Automated Personal Assistants Kai A. Olsen and Alessio Malizia

### DEPARTMENTS

- **Elsewhere in the CS** 4

- 78 **Computer Society Information**

- 94 **Career Opportunities**

Reuse Rights and Reprint Permissions: Educational or personal use of this material is permitted without fee, provided such use: 1) is not made for profit; 2) includes this notice and a full citation to the original work on the first page of the copy; and 3) does not imply IEEE endorsement of any third-party products or services. Authors and their companies are permitted to post the accepted version of their IEEE-copyrighted material on their own Web servers without permission, provided that the IEEE copyright notice and a full citation to the original work appear on the first screen of the posted copy. An accepted manuscript is a version which As been revised by the author to incorporate review suggestions, but not the published version with copyediting, proofreading and formatting added by IEEE. For more information, please go to: <u>http://</u> www.ieee.org/publications\_standards/publications/rights/paperversionpolicy.html.

Permission to reprint/republish this material for commercial, advertising, or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to the IEEE Intellectual Property Rights Office, 445 Hoes Lane, Piscataway, NJ 08854-4141 or pubs-permissions@ieee.org, Copyright © 2011 IEEE. All rights reserved.

Abstracting and Library Use: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy for private use of patrons, provided the per-copy fee indicated in the code at the bottom of the first page is paid through the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923.

IEEE prohibits discrimination, harassment, and bullying. For more information, visit www.ieee.org/ web/aboutus/whatis/policies/p9-26.html.

retugmed

**ELSEWHERE IN THE CS**

# **Computer Highlights Society Magazines**

he IEEE Computer Society offers a lineup of 12 peer-reviewed technical magazines that cover cutting-edge topics in computing including scientific applications, design and test, security, Internet computing, machine intelligence, digital graphics, and computer history. Select articles from recent issues of Computer Society magazines are highlighted below.

Lateness is the most common form of software project failure. Its causes can seem complex when viewed from ground level, but are surprisingly simple with a slightly more distanced perspective. In "All Late Projects Are the Same" in Software's November/December issue, Tom DeMarco says that what's really wrong with software folks is that they are continually beating themselves up for something that's somebody else's fault. DeMarco asserts that the louder the complaints about project lateness, the more likely it is that the project set out to deliver marginal value and was therefore kicked off under the false premise that it could be completed on the cheap.

# lintelligent Systems

To help people live better in today's digitally explosive environment, the authors of "Cyber-Individual Meets Brain Informatics" in the September/October issue of IS envision a Cyber-Individual (Cyber-I) that is the counterpart of a real individual in the physical world. Brain informatics, an emerging interdisciplinary field that systematically studies the human information processing mechanism, provides the principles of individual modeling that guide Cyber-I's core design and intelligence upgrade. The Cyber-I is intended to create a powerful demand for brain informatics research on individual information-processing differences and provide a testbed for evaluating future results obtained from that research.

# Computer Graphics

In "Digital-Content Authoring" in CG&A's November/ December special issue, guest editors Takeo Igarashi of the University of Tokyo and Radomir Mech of Adobe introduce recent advances in digital-content-creation techniques, ranging from 3D modeling to behavior authoring and image editing. Although the articles in this special issue address diverse problems, they provide a good overview of techniques common to authoring problems in general.

# **Computing**

Given its leading role in high-performance computing for modeling and simulation, the US Department of Energy has a tremendous need for data-intensive science. The datasets it generates significantly outstrip current analysis capabilities. More comprehensive analysis would help scientists discover and identify unanticipated phenomena and expose shortcomings in current simulation methodologies and software. Also, realtime data analysis would enable intelligent design and refinement of experimental processes. "Data-Intensive Science in the US DoE: Case Studies and Future Challenges" in the November/December issue of CiSE locates the challenges and commonalities among three case studies and illuminates, in detail, the technical challenges involved in realizing data-intensive science.

# SECURITY & PRIVACY

S&P's September/October special issue on cyberwarfare addresses the use of cyberattacks as an instrument of warfare. The four papers selected for the issue, introduced by guest editors Thomas A. Berson of Anagram Laboratories and Dorothy E. Denning of the US Naval Postgraduate School, address topics relating to the use of cybermilitias in cyberwarfare, policy and legal issues concerning state use of cybercapabilities, military principles for conducting cyberwarfare, and

Published by the IEEE Computer Society

0018-9162/11/\$26.00 © 2011 IEEE

Previous Page | Contents | Zoom in | Zoom out | Front Cover | Search Issue | Next Page

strategic deterrence of cyberattacks against national infrastructure.

# ervasive

Much research into pervasive computing has been devoted to systems comprising a small number of devices that interact with a single individual or a small group of users. Body-worn sensors and sensors embedded in the user's environment are used to infer user location, activity, and information about the user's immediate surroundings, shaping the concept of context awareness. In the October-December issue of PvC, guest editors Paul Lukowicz, Tanzeem Choudhury, and Hans Gellersen assert that as technology becomes truly pervasive, we must proceed from the "single user, single system" perspective to largescale heterogeneous systems that involve many devices and many individuals collaborating across different spatial and temporal scales.

# **Internet** Computing

In IC's September/October issue, guest editor Craig W. Thompson of the University of Arkansas introduces nine articles on virtual world architectures-seven in the current issue and two to appear in future issues. The articles explore the current limitations of virtual worlds, deconstruct their architectures, and consider how the architectures might evolve to extend the technology's applications. Topics include the integration of 3D virtual world viewers with Web browsers as well as the federation and extension of virtual worlds, their accuracy, and relevant standards.

Although general-purpose CPUs have traditionally been the dominant player in both mainstream and highperformance computing systems, recent years have seen a major shift toward GPUs. Originally developed primarily for graphics and video applications, researchers are increasingly harnessing GPUs by using programming languages such as CUDA and OpenCL to provide large performance speedups for general-purpose applications. Guest editor David Brooks of Harvard University introduces Micro's September/October special issue on GPUs versus CPUs with a discussion of advances and challenges in the field of hybrid CPU/GPU computing.

# **MultiMedia**

The July-September issue of MultiMedia features an article titled "Mobile Visual Search: Architectures, Technologies, and the Emerging MPEG Standard" in which authors from Stanford University, Nokia Research Center, and Qualcomm review current mobile-search architectures and key component technologies. They also review MPEG activity to define a working draft for a new visual-search standard in the mobile context by February 2012.

# Professional

Guest editors for the September/October special issue of IT Pro present six articles on the future of Web applications. According to their introduction, "In the coming years, billions of devices will be connected to the Internet, and they'll access and share information through the Web." Three articles focus on Web app development, one on digital diaries as an application scenario, one on the cloud computing ecosystem, and the sixth on the shrinking boundary between mobile and Web applications.

### Multimedia Web Extras

Computer's November multimedia-enhanced digital edition includes the content listed below. You can also find these items online at www.computer.org/ computer-multimedia.

### Codesign for InfiniBand Clusters

Sreeram Potluri, one of the authors of "Codesign for InfiniBand Clusters," shares a deeper look into how the InfiniBand cluster works.

### Extreme-Scale Computing

In an interview conducted during a recent meeting of the IEEE Computer Society's Magazine Operations Committee, Loyola University's George K. Thiruvathukal describes exascale, or extreme-scale, computing and some of its design challenges.

### The History of Supercomputing Research

Larry Smarr, founding director of the National Center for Supercomputing Applications, provides a brief background into the history of supercomputing research.

### The Known World (Behind the Scenes)

David Alan Grier gives a behind-the-scenes look at how he composes his popular "The Known World" column for Computer.

### Tips for Patent Applicants

A podcast episode based on an article published in Computer's September 2011 issue reviews basic points to keep in mind once you've successfully filed for a patent.

refugmed

THE KNOWN WORLD

# The Honest Give-and-Take

David Alan Grier George Washington University

Information technology has not only expanded the scale and scope of global markets, it has also provided the means for probing the meaning of every give-and-take transaction.

he e-mail quickly became a constant nag, a dark angel visitant to remind me of my wrongs. Each time, it asked if I would evaluate my recent automobile purchase at Mr. Tony Pro's Auto Mall. Each time, I replied with a flick of the delete key. I was in no mood to give Mr. Pro any information that might strengthen his hold on me.

Under the best of circumstances. the negotiations over a new car are fraught with inequalities and offer all the advantages to the seller. The sticker price is a fiction. The invoice is no closer to the truth, as a regional office pays incentives on each car sold to better control of flow of products from factory to market. Every bit of information about automotive preferences or driving habits gives a chit of power to the dealer.

Often, the customer has no greater power than bluff and bluster, both of which were factors in my negotiation. However, while most customers buy a car only once every few years-or in my case, 14 years-the seller has the dominant position, having ample experience in offering a ready defense that sports a strong handshake, a firm smile, and a protest that he's doing all he can for you.

So when the honest give-andtake was done, and the new car was parked in front of my house, I was in no mood to give Mr. Pro any more information than was necessary. Although he could protest with all his might that he was merely trying to serve me better, I nevertheless harbored the fear that he was trying to gain the upper hand in a future market transaction.

### THE VALIDITY AND THE VALUE

Information technology has not only expanded the scale and scope of global markets, it has also provided the means for probing the meaning of every give-and-take, for determining if the bargain was valid and if the result was valuable.

Although they're often treated as if they were the same thing, validity and value are very different concepts, Valid activities are those that are done well, that follow basic principles, that demonstrate the truth of the underlying concepts. Valuable activities are those that are important: they expand the field, find application to other disciplines, or generate a flow of money from satisfied customers.

As engineers, we tend to use experts to determine validity and markets to assign value. Experts review new ideas, test their underlying assumptions, and analyze how they were produced. If the results of this effort meet their standards, the experts declare the idea valid. Things can change. The field can evolve. However, as far as the experts can determine, the new idea is a valid addition to the body of knowledge.

In assigning value, markets look beyond validity. An idea can be clever, be completely valid, and represent a substantial intellectual achievement. but still have no value whatsoever. Value need not be measured in terms of the profit a concept can produce in the public market or the numbers of workers its production can employ. An idea can be valuable if it provides tools that expand the field, has applications to other technical subjects, or merely simplifies the task of creating other new ideas.

Yet, markets are influenced by human factors that can temporarily mask value. One party can completely mislead the other into assigning an inflated value to a product. Those who work in the marketplace, such as those who offer automobiles for

retuqmo2

sale, need to protect their decisions by controlling the flow of information with a paired set of marketing tools: the suggestion system and the recommendation system.

### SOLICITING SUGGESTIONS

Suggestion systems search for valuable ideas from customers or employees. Recommendation systems present ideas with the intent that customers or employees will find value in them. Both have long histories that could probably be traced, with little difficulty, to transactions on the Silk Road. However, both have been the object of careful analytic study and engineering practice. They show how we systematically try to extract or create ideas.

Suggestion systems are processes that solicit feedback from customers or employees. They're characterized by the familiar, although commonly mocked, suggestion box, usually a container with a slot in its top that accepts slips of paper offering new ideas. With the rise of the modern factory, suggestion systems acquired the trappings of an engineering discipline. They had a theory of operations, a set of best practices, and a professional society, the National Association of Suggestion Systems, which was located in downtown Chicago.

By the middle of the 20th century, the directors of NASS felt that their technology had become crucial to modern industrial management. "Having once and for all demonstrated its undeniable worth," they explained, "the Suggestion System is here to stay, to flourish and thrive and add its full, fair quota to the steady onward march of American Progress through the years."

The standard model for suggestion systems was fairly straightforward. A suggestion box collected ideas from customers or workers. These ideas were sorted by a suggestion clerk, who took them to the appropriate managers for validation. These managers determined if the suggestions were valid and estimated the amount of money that might be earned or saved from each. From this review, the validated suggestions moved to a senior manager or operations committee, who determined the value of each suggestion by looking at the potential income or savings in the context of the entire company. They selected the most valuable suggestions for implementation and rewarded the individuals who had put their ideas in the box.

Despite its confidence in suggestion systems, NASS was forced to admit that suggestion systems often failed to produce any value for

**Both suggestion** systems and recommendation systems have been the object of careful analytic study and engineering practice.

the company. These systems were often expensive to operate and often met resistance from managers and engineers.

World War II produced the one brief period when suggestion systems were effective. It was no ordinary time. Many managers were open to the suggestions of outsiders as they were in new leadership roles and had no stake in existing production or operational systems. All felt the urgency of the war. Many, if not most, had relatives or neighbors in combat. By the middle of the conflict, all war production plants were required "to provide machinery whereby each man may submit ideas and suggestions for doing the job better." This requirement came with the promise that these systems would "tap a vast new reservoir of ideas, welding our productive genius into a united effort for victory."

Yet, suggestion systems died a quick public death after the war. NASS declared that "nearly 95 percent of all attempts to operate suggestion systems were unsuccessful." Although the organization continued operations for a decade, it then disappeared.

Suggestion systems soon became objects of ridicule by the public. Cartoons showed suggestion boxes sitting over trash cans, shredders, and toilets. The Computer Society's suggestion box currently sits locked on a lunchroom shelf. No one knows what might be in the box or where the key might be.

### SUGGESTIONS TO RECOMMENDATIONS

The Internet has considerably simplified the process of soliciting and organizing suggestions. Questionnaires can be sent by mail and collated into a central database. Ideas can be sent to managers for required validations. The news of a successful idea can be spread to entire workforces or customer populations. Modern technology has turned the suggestion system into the recommendation system-the software that gathers data on customers and identifies products that each might find valuable.

Recommendation systems, sometimes known as collaborative filtering systems, have proven more valuable than their progenitors. Most large Internet retailers have embraced such systems. It's unusual to purchase items without being told what others have bought, what offerings go well with our selections, or what new product might be of interest to us. One major retailer, Netflix, even sponsored a contest to develop a new recommendation algorithm and, in 2009, rewarded an approach that it identified as a substantial improvement over the prior state of the art.

Recommendation systems have succeeded where suggestions systems did not for a pair of fundamental reasons. First, they address the problems of mass consumption,

### THE KNOWN WORLD

which are often simpler to grasp and easier to manipulate than the problems of mass production or mass distribution, which were the common focus of suggestion systems. Second, they exploit one of the fundamental strengths of information processing: the ability to record what we actually do, rather than the ideas we propose.

According to a recent survey of the technology, most recommendation systems utilize four types of data. Only the first, rating data, comes from the sort of questionnaires the auto dealership asked me to complete. The remainder is data that describes us-that is, demographic data-or data that describes our actions in the marketplace, such as behavior or transaction data. It's one thing to provide misleading responses on a questionnaire, as it only means that we're lying to others. It's quite something else to engage in misleading market behavior, as such actions mean that we're lying to ourselves.

### **ACTIONS RATHER THAN** WORDS

For the questions from Mr. Tony Pro's business, I provided the most useless of lies. I scrolled through his form and checked the neutral rating of 4 for each query. However, he ultimately turned the tables on me by capturing a little bit of my identity. After completing the questionnaire, his system began to bombard me with notices to have my new car checked by his skilled mechanics. The notices ranged from enticing to threatening, from promising new features for the car to threatening to void the warranty should I drive far more than the engineering specifications recommended.

One day, I received a notice that I would get a free tune-up if I took the car to the shop in the middle of the week. It was a little hook that deftly hid the great truth that there's nothing offered for free in this world that doesn't require payment at some future date. After delivering my car to the dealership, I found a chair in the corner of the showroom, where I began to work on some research on my laptop.

After 20 or 30 minutes, an emplovee asked me if I would like to use the wireless connection. Grateful for the opportunity, I accepted his offer and then asked him about his job at the dealership. I indicated that I had worked for the auto industry during my college years and was interested in how the work might have changed.

"I'm the data mechanic," my new friend replied.

# Intelligent ≝Systems

THE #1 ARTIFICIAL INTELLIGENCE **MAGAZINE!**

IEEE Intelligent Systems delivers the latest peer-reviewed research on all aspects of artificial intelligence, focusing on practical, fielded applications. Contributors include leading experts in

- Intelligent Agents

The Semantic Web

- Natural Language Processing

- Robotics

Machine Learning

Visit us on the Web at www.computer.org/intelligent

"Data mechanic?" I asked. "Does that mean you manage the computers and networks in the office?"

"Yes," he responded, "and also the diagnostic and data collection systems in the shop."

A moment passed before I realized what he had told me. My car was sitting in a mechanic's stall, freely volunteering my habits as an owner and driver. It couldn't quite reveal every detail about every trip, but it could download information about the number of miles I had driven, the range of my travels, and the way I operated the car. Perhaps I hit the brakes too hard. Maybe I accelerated too fast from a stopped position. Most likely I dawdled on the freeway, forcing others into a line behind me. All of this information, every little bit, was being relayed to the employees of Mr. Tony Pro.

fter this first visit, the e-mails from Mr. Tony Pro changed their tone. Where they once suggested that I might be driving the car too much between visits, they now touted the value of maintaining low-mileage vehicles. He had clearly learned something from my car. He knew that I lived in the city and rarely drove during the week. The information that I had so carefully avoided providing to him in a questionnaire or during an exchange with his employees had been captured from my car's memory and now found a home in Mr. Pro's records. He gained one more chit that day in the economic giveand-take. C

David Alan Grier, an associate professor of international science and technology policy at George Washington University, is the author of the upcoming book, The Company We Keep. Contact him at grier@gwu.edu.

Selected CS articles and columns cn are available for free at http://ComputingNow.computer.org.

Previous Page | Contents | Zoom in | Zoom out | Front Cover | Search Issue | Next Page

### 32 & 16 YEARS AGO

### **NOVEMBER 1979**

HEALTHCARE (p. 4) "While computer technology offers a unique resource for containing costs and improving the quality and availability of care, many government officials, health research planners, concerned citizens, and even computer professionals claim that medical computing has increased costs while offering insufficient proof of improved health care. They are skeptical of the positive contributions information technology can make to cost containment and cite poor performances by computer designers over the last decade, who overestimated the power of the technology and underestimated the complexity of health care systems."

AMBULATORY PATIENTS (p. 9) "For the past decade the Laboratory of Computer Science of the Massachusetts General Hospital has been involved in the development and implementation of a computer-based medical information system, COSTAR (for computer-stored ambulatory record). Designed to perform the data management functions needed by a group practice in the care of ambulatory patients, COSTAR supplements or replaces the traditional paper-based patient medical record with an integrated information system. COSTAR data management meets the medical, administrative and financial needs of ambulatory group practice, and can be adapted to meet the requirements of other group practices. COSTAR systems are now operational or being installed in over a dozen practices in the United States or abroad."

HOSPITAL MANAGEMENT (p. 28) "MATRIX ... is an on-line data base management system designed to allow hospitals to develop customized information systems for areas such as the ordering of medications and tests and the updating of patient records. The objectives of MATRIX ... are to improve the quality and lower the cost of patient care. It is designed to provide sufficient flexibility to support applications unique to health care institutions and to evolve with changes in medicine and technology."

CLINICAL DATA BANKS (p. 34) "... Current data storage and retrieval technology should permit the development of large data banks representing collected clinical experience. These will aid the physician by linking specific treatments to health and medical processes and to patient outcome. ARAMIS, the American Rheumatism Association Medical Information System, is a national data bank for rheumatic diseases, a prototype for such systems. Its software (the Time-Oriented Databank System, or TOD) also supports national data banks in stroke and coma as well as smaller data bases in other specialties."

**ONCOLOGY MANAGEMENT** (p. 42) "The Johns Hopkins Oncology Center is one of 21 Comprehensive Cancer Centers

established as part of the National Cancer Plan initiated by the Cancer Act of 1971. The center has major programs in laboratory and clinical

research, education, and collaborative activities with community physicians. ... At any one time, there are 1500 patients being treated under one or more of several hundred formally established treatment plans called protocols. This article describes a clinical information system which assists in the management and care of these patients."

**COMPUTING IN CHINA** (p. 60) "A question frequently asked is 'How long will it take the Chinese to catch up with the industrialized nations?' In view of China's late arrival in the industrial age, the 10-year educational and managerial gap created by the Cultural Revolution, and the economic handicaps bedeviling the country, I believe the gap between China and the industrialized West could take as long as 30 years to close. China will make tremendous strides, but there is simply so much catching up to do that a significant closing of the gap will not come quickly. Thirty years, however, should give China time to become a formidable rival to the other industrialized nations of the world."

TELECONFERENCING (p. 62) "... The combination of a CAD system data file and graphic terminal obviously offers yet another means for interpersonal communication. By using an appropriate command language, interactive graphics teleconferencing by computer is possible. When combined with a dial-up voice connection, an audio/graphics teleconferencing arrangement can offer participants both the ability to view the highest quality of drawings and the opportunity to discuss, edit, or exchange them."

RELIABILITY TOOLS (p. 77) "The gap between DP hardware and software is taking on the dimensions of a canyon as hardware becomes cheaper, faster, and more reliable, and software becomes more expensive, cumbersome, and error-ridden. One of the reasons for the difference lies in the retention, in software design and development, of concepts and methodologies rooted in a dead past. So-called reliability tools are among the worst offenders in this regard."

Editor: Neville Holmes; neville.holmes@utas.edu.au

0018-9162/11/\$26.00 © 2011 IEEE

### 32 & 16 YEARS AGO

### **NOVEMBER 1995**

**DEPENDABILITY** (p. 5) "The implications for the future directions of software are interesting. There will be increased emphasis on fault-tolerant and highly available systems. Diagnosis and delivery of software fixes on line (from your car's electronic computers to upgrades for your ISDN phone service and modem) will come into vogue. ... New products consisting of 'middleware' between the operating system and application software will be created to ensure that applications and data don't crash or fail in a way that compromises use. Parallel databases, fault tolerant servers and networks, and selfhealing computers will become the platforms necessary to deliver software."

PERFORMANCE TOOLS (p. 21) "The primary motivation for using parallel computer systems is their high performance potential, but that potential is notoriously difficult to realize, and users often must analyze and tune parallel program performance. Parallel systems can be instrumented to provide ample feedback on program behavior, but because of the volume and complexity of the resulting performance data, interpreting these systems can be extremely difficult. Hence, performance tools are needed to help bridge the gap between raw performance data and significant performance improvements."

**PERFORMANCE PREDICTION** (p. 47) "Other problems, such as perturbation of the program's behavior and generation of vast seas of (mostly useless) data that require a performance expert to interpret, make performance analysis a tedious, error-prone, and time-consuming task. Performance prediction tools can significantly expedite this task by providing fast and accurate information to guide the programmer toward efficient data distribution strategies and/or profitable program transformations that will increase performance."

EVENT TRACING (p. 57) "Just as a logic analyzer lets a hardware designer study signal transitions, software event tracing provides the raw performance data needed to understand all possible spatial and temporal interactions of parallel tasks. However, on parallel systems with hundreds of processors, application instrumentation of procedure calls, message passing, and input/output can quickly generate a large amount of performance data. ..."

WWW SERVERS (p. 68) "To support continued growth, WWW servers must manage a multigigabyte (in some instances a multiterabyte) database of multimedia information while concurrently serving multiple request streams. This places demands on the servers' underlying operating systems and file systems that lie far outside today's normal operating regime. Simply put, WWW servers must become more adaptive and intelligent. The first step on this path is understanding extant access patterns and responses. ..."

NETWORK AS COMPUTER (p. 81) "Having usurped much of the mini and mainframe domain, the PC now faces a serious challenge to its dominance on the desktop computing scene. Larry Ellison, CEO of Oracle Corp., has referred to the PC as ' a ridiculous device' and is not alone in viewing the Internet as a rising star that will push the PC out of the spotlight and into a supporting role. Sun Microsystems, which has long maintained that ' the network is the computer,' has thrown down the gauntlet by developing a product that can only accelerate this trend: a network programming language called Java."

BACKFIRING (p. 87) "The availability of empirical data from projects that use both function-point and lines-of-code metrics has led to a useful technique called 'backfiring.' Backfiring is the direct mathematical conversion of LOC data into equivalent function-point data. Because the backfiring equations are bidirectional, they also provide a powerful way of sizing, or predicting, source-code volume for any known programming language or combination of languages."

A NEW STANDARD (p. 89) "... While software has been established as an integral part of scientific and business disciplines, environments for developing and managing software have proliferated without a common, uniform framework for the software life cycle. This standard provides such a framework, so that software practitioners can 'speak the same language' when they create and manage software. Practitioners can use the framework to acquire, supply, develop, operate, and maintain software."

MUSIC (p. 91) "Since 1992, the IEEE Computer Society has supported the establishment of a Technical Committee on Computer-Generated Music. This vast interdisciplinary area of computer science and electrical engineering stretches from artistic music composed or played with computers to audio signal processing. CGM offers new possibilities for research and practice, and as the IEEE CS has argued, this signifies CGM's greater importance in science and technology-not to mention music itself."

PDFs of the articles and departments from Computer's November 1979 and 1995 issues are available through the IEEE Computer Society's website: www.computer.org/ computer.

Previous Page | Contents | Zoom in | Zoom out | Front Cover | Search Issue | Next Page

**TECHNOLOGY NEWS**

# **Turning on the** Lights for Wireless **Communications**

Lee Garber

In the ongoing search for better ways to transmit data, researchers have turned to a wireless approach that has been discussed for years: visible light communications.

esearchers in industry and academia are always looking for newer, faster, and more energy-efficient approaches to communications. In their search, they have turned not to a new technology but to one more than 130 years old: visible light communications.

VLC uses modulated light signals rather than radio frequency (RF), microwave, or other types of signals to transmit data.

As the "VLC Projects and Products" sidebar discusses, not only are academic and corporate scientists developing VLC approaches, but several companies have already released products based on the technology. Vendors that have products or are in the process of developing them include Casio, Eurescom, France Telecom, NEC, Orange, Panasonic, Samsung, Sharp, Siemens AG, Telefonica, and Toshiba.

Schools with VLC research programs include the Sapienza University of Rome; Dortmund University of Technology; Ilmenau University of Technology; University of Athens; University of California,

Berkeley; and University of Oxford.

The technology could be utilized for purposes such as Internet access and various types of networking, as well as point-to-point, point-to-multipoint, and multipoint-to-point communications, explained University of Edinburgh professor Harald Haas.

Proponents say VLC offers several important advantages over current wireless systems including higher data rates, better security, more spectrum availability, and greater energy efficiency. They say the technology would be particularly useful in settings such as aviation, green computing, and healthcare facilities. The "Illuminating the Road Ahead" sidebar covers VLC implementation in more depth.

However, VLC also has weaknesses and faces obstacles to commercial success. Unlike Wi-Fi and numerous other wireless technologies, it is not yet proven in large-scale usage. In addition, VLC access points will have to be made affordable.

### **COMMUNICATING VIA LIGHT**

Alexander Graham Bell, the telephone's inventor, sent the first VLC transmission on 3 June 1880 via another one of his inventions: the Photophone. In 1931, Bell Telephone Laboratories engineer-and subsequent vice president-Sergius P. Grace proposed using light for secure wireless communications.

However, it was many years before work on VLC began in earnest.

### **Driving forces**

There are several reasons for the recent VLC push. For example, users are always looking for better performance, and VLC promises high data rates. Also, the technology works with LED lights, which are becoming increasingly popular.

Demand for wireless communications is continuing to increase, but the spectrum available for traditional, radio-based mobile approaches is shrinking rapidly.

Using radio communications equipment can be hazardous in various types of locations. For example, it can cause sparks, which makes it dangerous for use on oil platforms. And it can interfere with other radio equipment, which makes it inappropriate for use on aircraft.

Published by the IEEE Computer Society

Π

Previous Page | Contents | Zoom in | Zoom out | Front Cover | Search Issue | Next Page

### **TECHNOLOGY NEWS**

# **VLC PROJECTS AND PRODUCTS**

here are numerous visible light communications research projects, and VLC products are even beginning to appear, signaling the technology's growing importance.

D-Light. University of Edinburgh professor Harald Haas has been working on VLC since 2004. Haas and his colleagues call their approach both D-Light (data light) and Li-Fi (light fidelity)

Haas expects his technology will be useful for purposes such as Internet access, vehicleto-vehicle communications, and machine-to-machine communications. He and his team plan to establish a spin-off company-VLC Ltd.-based on their research, which was funded by Scottish Enterprise, a government agency that works to stimulate economic growth in Scotland.

OMEGA. The European Union-funded OMEGA project—an interdisciplinary effort with participants from industry and academia that ran from 2008 to March 2011-researched user-friendly, high-bandwidth, home-area networks. The project explored options such as optical, power-line, infrared, and VLC networking.

OMEGA's VLC demonstration used 16 high-power, ceiling-mounted LED lamps. The researchers aggregated the output of four video players into an Ethernet stream, which they then modulated onto electrical current sent to the lamps. The lights then continuously broadcast four high-definition videos at 100 Mbits per second.

US National Science Foundation. The NSF operates the Smart Lighting Engineering Research Center in partnership with several US universities.

As part of this program, Boston University professor Thomas Little noted that he is working on a project that uses VLC to provide network connectivity and control among distributed light sensors. Little is also researching data-delivery approaches that use both VLC and radio communications.

RONJA. The Reasonable Optical Near Joint Access Free Space Optics device, which Czech Republic-based Twibright Labs developed, uses red light to transmit data up to 1.4 kilometers. It also uses infrared light, which has a wavelength longer than that of visible light, for transmissions up to 0.78 km.

Siemens. The German company is primarily developing high-speed VLC links based on commercial LEDs, focusing on modulation techniques, as well as LED-driver circuitry and analog receivers. Siemens has been working with one of the brightest LEDs available commercially, made by its Osram subsidiary.

Klipsch. This US manufacturer of sound equipment has introduced speakers that can receive music via data transmitted from LED lightbulbs.

The LightSpeaker system combines 10-watt LED lighting and a 20-watt wireless sound speaker into a unit that installs like a standard light bulb. A music source is plugged into a centrally located transmitter, which then sends different music streams to as many as four pairs of speakers.

LVX System. The company has developed an LED lighting fixture that offers an access point to whichever network an individual or organization is using.

The system is installed as part of the 2 × 2 foot lighting panels used in many commercial buildings, although LVX hopes to offer the system in other fixture models soon, noted CEO John Pederson. Customers install a standard networking cable that plugs into a board on the back of the fixture.

The system's current data rate is 0.5 to 3 Mbps at distances up to 10 feet. Pederson said this is adequate in office and airport settings, the company's target markets. A secondgeneration system, available in a year, will offer higher speeds and programmability, he noted.

LVX System has installed its first few light fixtures in six municipal buildings in St. Cloud, Minnesota.

Doctors are increasingly using wireless technology to transmit data from medical devices to PCs or laptops for analysis. However, there are powerful magnetic fields around devices such as magnetic resonance imaging scanners, so physicians can't use radio-based wireless technology to transmit MRI data they collect.

### Under the hood

VLC uses high-frequency pulsed light instead of radio waves or other types of signals. Many of the implementations work with LEDs in

adapted standard sources such as indoor and outdoor lighting, as well as illuminated signs and displays, street lamps, and vehicle headlights.

System elements. A VLC system's key elements include a visible light source such as an LED lamp, which acts as the communications channel and transmitter; driving circuitry to control the light source; a modulator to get data onto the light stream; and a photodetector to receive the incoming stream and demodulate the information into electrical signals for processing, noted Siemens spokesperson Sebastian Webel.

According to the University of Edinburgh's Haas, the VLC system converts the electrical data signal it receives into a rapidly varying stream of photons. To modulate the signal, the driving circuitry varies the LED's light intensity at multiple levels.

Haas said his team uses "subcarrier index-modulated orthogonal frequency-division multiplexing (SIM-OFDM) to vary the light intensity in a very subtle and distinct fashion." This enables high data rates by transmitting at least 10 bits for each transmission step, as opposed to the one bit that simple on-off switching allows.

The signal is sent to the photodetector, where the light excites electrons and induces an electrical current. The data must undergo an electrical-to-optical-to-electrical conversion because there currently is "no practical means of high-speed, alloptical data processing," Webel said.

Finally, Haas added, an algorithm at the receiving end processes the data stream and converts it into the ones and zeros of digital data.

Light sources. VLC systems can work with either a single light source of a specific color or by combining red, green, and blue light sources to produce the desired color.

Different LED colors have different efficiencies, interference levels, and manufacturing costs, noted Boston University professor Thomas Little.

Omag

Most lighting-quality LEDs use blue LEDs with phosphor to create a white color, a relatively inexpensive approach that offers only one transmission channel per data stream. Mixed-color LEDs are more complex but offer multiple transmission channels in a single stream.

Using a bright LED reduces the number of lights necessary to provide the same signal strength, said Webel. However, he added, the challenge is that bright LEDs require high driving currents, which means researchers must develop new driver-circuit architectures.

Increasing throughput. VLC systems can increase throughput by creating multiple communication channels within a single light stream via the use of different colors of light or different modulation frequencies, Webel noted

For example, SIM-OFDM can convert a serial data stream into many-perhaps 1,000 or moreparallel streams based on frequency.

Using multiple LEDs and photodetectors as transmitters and receivers, respectively, can further increase throughput, he added. This gives users the option of simultaneously sending separate data streams over each LED. In some cases, multiple LEDs are required just to provide the necessary lighting intensity.

Data rates. VLC throughput is increasing. A near-term goal of researchers is to achieve data rates of 100 Mbits per second.

The fastest Wi-Fi version, IEEE 802.11n. offers theoretical-maximum data rates of about 150 Mbps, although using OFDM along with multiple transmitters and receivers, could boost the speed to 300 Mbps. Long-Term Evolution (LTE), which some vendors market as fourth-generation cellular technology, can theoretically transmit up to about 300 Mbps.

A VLC system that Germany's Siemens and Heinrich Hertz Institute developed has transmitted data at

retuqmo2

### **ILLUMINATING THE ROAD AHEAD**

f and when visible light communications is implemented more widely, it could be used in many settings and for many purposes:

Healthcare. Because, unlike radio communications, VLC doesn't experience problems with magnetic interference, the technology could enable doctors to wirelessly transmit data from magnetic-based medical devices, such as MRIs, to PCs or laptops for analysis.

Hazardous settings. VLC could enable wireless data communications in oil fields and mines, near gas pipelines, and in other environments where using RF equipment—which can create sparks—could be dangerous.

Commercial aviation. Because, unlike radio communications, VLC doesn't interfere with flight-related radio signals, it could enable wireless data communications by passengers on aircraft. Airlines generally don't let passengers use RF-based equipment on planes when in flight. VLC could also let airlines wirelessly offer entertainment and other content to passengers.

Green computing. VLC offers more energy efficiency than radio communications.

Military applications. VLC could enable fast, secure transmissions within vehicles and aircraft.

Underwater communications. RF doesn't work optimally underwater, but VLC functions well in such settings over short distances.

Automobiles. LED stoplights or railroad signals could transmit information to cars or trains. Cars could use LED lights to help occupants communicate with other vehicles, noted Siemens spokesperson Sebastian Webel.

Smart lighting. This approach, designed to create intelligent lighting systems that can be operated in an energy-efficient way, could use VLC as the infrastructure for illumination, control, and communications. VLC would require less wiring and energy than typical smart-lighting systems.

Sensors. VLC could be useful for communications in various types of sensor systems, noted Boston University professor Thomas Little.

Museums. VLC systems could illuminate an object in an exhibit and at the same time wirelessly provide information about it, noted University of Edinburgh professor Harald Haas.

about 500 Mbps over a range of a few dozen centimeters. Earlier experiments demonstrated data rates of 200 Mbps over a distance of 5 meters.

The researchers used a bright LED that they could modulate at a frequency at least twice as high as other LEDs that they tested. Webel said the higher frequency enabled greater data rates, although researchers are unsure why this is the case.

Haas said his research team hopes to achieve data rates up to 1 Gbps in nonlaboratory settings by late 2012.

### Advantages

VLC offers several advantages over traditional, radio-based wireless systems.

Security. VLC is generally more secure than traditional RF technologies, according to Haas. First, only receivers within the visible cone of transmitted light can receive data, making transmissions difficult to intercept.

Also, Haas said, walls and other obstacles can block the highfrequency VLC transmissions, meaning data is unlikely to leak out of an office or home.

Energy efficiency. VLC systems use less power in transmitting data than radio-based communications equipment. VLC doesn't use many of the types of energy-consuming communications equipment that radio-based systems employ, such as antennas and radio circuitry, Haas noted. In fact, he said, VLC's primary power-consuming element consists of the energy-efficient LED lights that are often already in operation.

VLC will also increase the demand for LED lighting, Haas added, which is more efficient than traditional fluorescent or incandescent sources.

### TECHNOLOGY NEWS

### Wider spectrum, more capacity.

There is much more visible light spectrum available than radio spectrum. The visible light spectrum extends from 400 to 790 THz, while the RF spectrum runs only from 3 KHz to 300 GHz.

Also, visible light doesn't have the shortage of available spectrum that radio-based wireless technologies are experiencing because of the growing use of mobile technologies, Boston University's Little said.

Although not all the visible light spectrum is optimal for communications, it still provides more opportunities than the RF spectrum for sending data without interfering with other communications.

### **POSSIBLE SHADOWS**

Radio technology already works well and meets most wireless users'

needs, Siemens' Webel said, Thus, he explained, VLC proponents will need to either offer better services than RF or find novel applications.

VLC has not been widely used for nearly as long as Wi-Fi and other wireless technologies. This lack of maturity could hurt VLC adoption, at least for a few years.

Another challenge will be developing VLC technologies that don't add much cost to lighting systems, Little said. For potential vendors, the University of Edinburgh's Haas noted, finding investors and pilot-program customers to get the technology moving commercially could be a chore.

A key issue for widespread VLC implementation is making the access points inexpensive enough to compete with other wireless technologies' base stations.

VLC works best when the light intensity is high, which means longdistance transmissions or those that could be at least partially blocked by obstacles or weather conditions could be problematic. This could make VLC less useful for longer-range outdoor applications, or applications that must work between buildings or between multiple offices or rooms within a building.

VLC could be subject to regulation as both a communications and a noncommunications technology, involving issues such as eye safety and illumination in traffic signals or car lighting. Proponents thus face the challenge of coordinating implementation across multiple types of standards and regulatory bodies.

endors could develop hybrid systems, using VLC when lineof-sight, visibility, and other conditions are favorable, and using RF technology at other times.

Haas predicted VLC will become popular because LED-lighting usage will increase. He noted that numerous countries have already banned incandescent light bulbs because of their energy inefficiency.

One of VLC's first commercial uses might be in applications requiring high-speed data transfer over short distances, such as file sharing, according to Little.

The technology will be popular where security is important and radio communications either are prohibited or face spectrum crowding, he added.

Editor: Lee Garber, Computer; l.garber@computer.org

cn

Selected CS articles and columns are available for free at http:// ComputingNow.computer.org.

Omags

Previous Page | Contents | Zoom in | Zoom out | Front Cover | Search Issue | Next Page

### **NEWS BRIEFS**

### **System Identifies User Location without GPS** or Wi-Fi

A Switzerland-based semiconductor vendor has developed a system for mobile devices that determines a user's location when neither GPS nor Wi-Fi is available. This could be valuable for users inside buildings in crowded urban downtown areas or in mountainous or heavily forested regions.

STMicroelectronics' system starts by taking input from three small, high-performance microelectromechanical systems, each on its own chip: a gyroscope, a compass-like sensor that measures the Earth's magnetic fields, and a sensor that estimates the user's altitude based on air-pressure readings.

Using multiple sensors provides enhanced motion- and location-based capabilities, said Benedetto Vigna, group vice president and general manager of STMicroelectronics' MEMS, Sensors, and High-Performance Analog Division.

The product employs a dedicated processor, along with STMicroelectronics' iNEMO filtering and predictive software engine, to integrate the different types of location-based information. It then utilizes dead reckoning to calculate users' positions in three dimensions (including altitude).

The technology yields information on users' linear acceleration, angular velocity, heading, and altitude. This enables them to identify the direction in which they're heading and their location.

According to STMicroelectronics, the system was designed to be energy-efficient, an important factor for battery-powered smartphones and other mobile devices.

The geomagnetic module-which measures  $3 \times 5 \times 1$  mm—offers high-resolution, three-axis sensing of linear and magnetic motion.

The 3-axis digital gyroscope measures 4  $\times$  4  $\times$  1 mm and doesn't require continuous communication between the sensor and the host processor, which reduces power consumption.

The air-pressure sensor measures  $3 \times 3 \times 1$  mm, operates at between 700 meters below and 10,000 m above sea level, and can recognize altitude changes as small as 0.3 m.

### Malware Infects US Military Drone System

A virus has infected the system behind American Predator and Reaper military drones.

Initially, US Air Force officials expressed fear the virus could log the keystrokes of the aircraft's remote pilots, creating the possibility that hackers could obtain and sell or otherwise distribute classified information.

However, military cybersecurity specialists now explain, the virus was a common type of malware that steals online gaming logins and passwords. Thus, they say, the malware probably wasn't part of an attack targeting the drones. Instead, it may have worked its way from other systems onto the US Department of Defense (DoD) networks

Air Force officials noted that the malware infected ground systems that are separate from the drones' flight controls and did not affect their operations. Thus, even after the virus was found, pilots continued to fly the drones, which the US military has used frequently in Afghanistan and Iraq.

The DoD's Host-Based Security System—a COTS-based application designed to monitor, detect, and counter known cyberthreats-found the malware recently.

Officials said that despite numerous efforts, they couldn't remove it from the computers at Creech Air Force Base in Nevada that control the aircraft. Instead, they had had to erase and reformat the drives that the drones' control systems use, a time-consuming process.

The malware incident isn't the drones' first identified security

STMicroelectronics has developed a product that uses three chip-based systemsa gyroscope, a compass-like sensor that measures the Earth's magnetic fields, and a sensor that estimates the user's altitude based on air-pressure readings—to determine a mobile-device user's location.

Previous Page | Contents | Zoom in | Zoom out | Front Cover | Search Issue | Next Page

**NEWS BRIEFS**

### **NEW TRANSISTOR COULD LET DEVICES INTERACT DIRECTLY WITH LIVING THINGS**

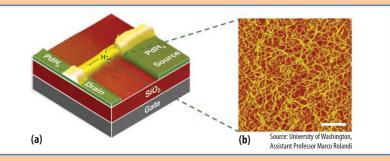

niversity of Washington scientists have built a transistor that uses protons to send information, potentially allowing the creation of devices that could communicate with living things. Such devices could monitor biological processes and eventually transmit signals that could control various functions.

Researchers are interested in using devices that can work directly with, for example, the human body, to help enable biological sensing or more effective prosthetics.

Electronic devices transmit information using electrons. Living things, on the other hand, use ions, which are positively or negatively charged atoms. Protons are positively charged hydrogen ions.

The challenge is finding a way to translate electronic signals into ionic and protonic ones and vice versa, noted assistant professor Marco Rolandi, the project's lead researcher.

"We found a biomaterial that is very good at conducting protons and allows the potential for interfacing with living systems," Rolandi said.

The University of Washington researchers developed a 5-micron-wide field-effect transistor that sends pulses of proton current.

"In our device, large bioinspired molecules can move protons, and a proton current can be switched on and off in a way that's completely analogous to an electronic current in any other field-effect transistor," Rolandi explained.

The device is made with maleic-chitosan, a substance typically obtained commercially from chitin, the structural element in crustaceans' external skeletons. According to the researchers, the material is easily obtained, simple to work with, and compatible with living tissue.

They also note that chitosan absorbs water and forms multiple hydrogen bonds within a transistor over which protons can easily hop.

The current prototype has a silicon base and thus couldn't be placed into a human body. However, the use of a biocompatible base could enable such implantation in the distant future.

University of Washington researchers have developed a protonic field-effect transistor (a) that uses protons to send information, which potentially allows the creation of devices that could communicate with living things. In the transistor, a voltage applied between the proton-transparent palladium hydride (PdHx) source and drain initiates a protoniccurrent flow along the maleic-chitosan channel, shown in yellow. When hydrated, maleicchitosan nanofibers (b) form an extended hydrogen bond network along which protons hop. An electrostatic potential applied to the gate electrode turns the protonic current on or off.

problem. For example, many of the aircraft don't encrypt the video they transmit to US forces. In 2009, soldiers found hours of footage shot by drones on the laptops of captured Iraqi insurgents.

Supposedly, the drones' cockpits are not connected to the Internet, which should make them unable to transmit captured keystrokes to a

hacker and leave them immune from transmitted malware. In the past, though, the use of external storage drives has introduced problems to military networks.

Several years ago, experts say a worm infected Predator and Reaper drones via the removable hard drives that load map updates and transportmission videos from one computer

to another. The DoD has ordered all drone units to stop using the drives.

### **New Technique Doubles Mobile-Network Throughput**

Rice University researchers say they've developed a full-duplex wireless technology that could double network throughput inexpensively without requiring new hardware for devices or networks and without causing service interruptions.

Currently, mobile networks require devices to use different frequencies to send and receive data. Full-duplex technology lets mobile devices send and receive data on the same frequency, effectively doubling a network's capacity.

The Rice scientists-led by Ashutosh Sabharwal, associate professor of electrical and computer engineering-demonstrated that device makers could reliably add fullduplex to existing smartphones and still maintain signal quality.

The researchers added full-duplex as an additional mode to the existing hardware, meaning that device makers wouldn't be required to add new hardware.

Said Sabharwal. "Device makers love this because real estate inside mobile devices is at a premium."

In the past, the concern with using the same frequency to send and receive data was that the dual sets of transmissions would interfere with accurate reception of incoming signals.

The Rice researchers overcame this by repurposing an existing antenna that devices currently utilize for multiple-input, multiple-output technology. MIMO uses several transmitters and receivers, rather than just one of each, to increase wireless throughput. With MIMO, multiple signals that the Rice system transmits cancel each other out, enabling the recipient to accurately receive what's being sent.

Sabharwal said his team will add the full-duplex technology into

Previous Page | Contents | Zoom in | Zoom out | Front Cover | Search Issue | Next Page

its wireless open access research platform, which is available to other scientists.

Although full-duplex wireless technology doesn't necessitate new cell towers, it would require new industry standards.

Thus, the researchers say, it probably won't appear for several years, when carriers begin using fifthgeneration cellular technology. Major carriers are just beginning to roll out 4G networks.

The researchers say their work already has attracted the attention of wireless providers worldwide.

The Rice scientists also showed that full-duplex systems could operate in asynchronous mode, meaning that a node could begin to receive one signal while still transmitting another, further increasing throughput.

### **Scientists Unveil Haptic Pedestrian Navigation** System

Japanese researchers have developed a pedestrian navigation system that uses haptics so that users can watch where they're going and not have to look at maps or a navigational device. They say their Hapmap system could be particularly useful for the visually impaired.

Keio University and University of Tokyo scientists developed Hapmap, which provides subtle, complex cues that accurately let users follow a winding path's curves without having to watch the small, battery-powered device

Typically, pedestrian navigation systems are limited to simple cues such as "walk straight ahead," even if a pathway has many curves.

Hapmap's haptic output component, operated by a servo motor, resembles a small seesaw, which pushes into a user's hand. When the display tilts right or left, it tells the pedestrian to walk in the indicated direction. When the display doesn't tilt, the user walks straight ahead. The researchers say this gives users the

sensation of holding onto a railing that is guiding them along a path.

Hapmap includes a user-tracking system and motion-capture cameras to identify where the pedestrian is and which way a path is turning. This enables the system to automatically control the haptic feedback in real time and offer accurate, detailed navigational information.

In the future, the researchers hope to enable Hapmap use in conjunction with GPS and other navigation systems.

### Securing Implanted Medical **Devices from Hacking**

Academic researchers have developed a system designed to prevent hackers from attacking implantable electronic medical devices such as heart pacemakers.

MIT and University of Massachusetts Amherst scientists say their system would keep hackers from being able to affect an implantable device's operations or steal patient information.

They note that implanted devices such as pacemakers, defibrillators, and insulin pumps increasingly

include wireless communication capabilities, used for purposes such as remote monitoring and diagnosis.

Research has shown that it might be possible to exploit the wireless capabilities to send commands to a device or intercept data that it transmits, although no such incidents have been reported.

The scientists developed a transmitter they call a *shield*, which patients could wear around their neck or wrist. The shield relays messages between an implanted device and authorized endpoints. It uses techniques such as signal jamming and encrypted channels to secure the communications and thereby block the interception of messages and the issuance of commands

The researchers noted that the eventual commercial success of their technology would depend in part on how serious patients consider the threat of attack against their implanted devices.

Editor: Lee Garber, Computer; l.garber@computer.org

### 17 **NOVEMBER 2011**

Comp

Previous Page | Contents | Zoom in | Zoom out | Front Cover | Search Issue | Next Page

The IEEE Computer Society's next-generation flagship publication

# More value, more content, more resources

For computing professionals, keeping abreast of the industry's most exciting developments is a continuous process. Beginning in January, Computer Digital will offer you even more tools to accomplish that at no risk.

Computer Digital will deliver the same great peer-reviewed articles and columns as the print version of Computer. PLUS, it will be:

Mobile-Read the email-delivered issue anytime, anywhere, at your convenience-on your laptop, iPad, or other mobile device.

**Searchable**-Quickly find the latest information in your fields of interest. Access the digital archives, and save what's most relevant to you.

Linked-Click on table of contents links and instantly go to the articles you want to read first. Article links go